# Microcomputer Interfacing and Programming

## **Preface**

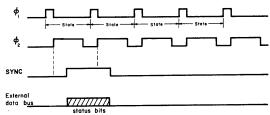

In 1971, the first microprocessor chips became commercially available. These were the Intel Corporation 4004 four-bit microprocessor chips which, while somewhat difficult to use in real computer applications, nevertheless did lead the way in control applications where they are still widely used today. The Intel 8008 eight-bit microprocessor followed quickly, and permitted the user to configure a small general-purpose "computer." At the time, several companies started to offer standard logic cards that had the necessary control logic, memory, and input/output buffers so that real applications could be tackled.

After the announcement of the 8008 chip, many semiconductor companies scrambled to get on the mciroprocessor bandwagon. Intel followed with their powerful 8080, Motorola with the 6800, Fairchild with the F-8, and so on through dozens of companies and microprocessor chips. Early in 1977, we witnessed a surge of "computer-on-a-chip" devices that contain, in a single integrated-circuit chip package, all the necessary logic, memory, and I/O capability to construct a small micro-

computer.

Not only are microcomputers finding widespread use in control and instrumentation applications, they have also spawned the hobby computer market. Five years ago, some hobbyists may have dreamed of having their own computers, but few had one. Now, thousands of ameteurs have small computers that are being used for general programming applications, playing games, providing real estate listings, maintaining inventories, and saving energy in the home. The publication of the Mark 8 construction article in *Radio-Electronics* in July 1974 started the flood. Based upon the 8008 microprocessor chip, the Mark 8 provided computer hobbyists with the means of having their own computer. Later followed by commercial models manufactured by MITS,

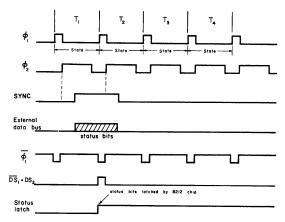

Inc., Southwest Technical Products Corp., Cromemco, Inc., IMSAI Manufacturing Corp., and many other companies, thousands of microcomputers can now be found in homes in the United States.

This is just the beginning. We can safely predict that home entertainment/communication centers based upon the marriage of television sets, LSI game chips, and microcomputers will be sold by the millions as a major consumer product within several years. If Congress and the FCC can come to grips with the communications revolution spawned by LSI technology and optical fibers, the next step will be expanded digital communications between homes, offices, and libraries.

Inexpensive microcomputers will eventually penetrate every facet of life. Today, they can be found in automobiles, sewing machines, microwave ovens, TV games, vending machines, gasoline pumps, taxi meters, and so on. Tomorrow, they will be in phones, washers, driers, typewriters, elevators, heating and cooling systems, children's toys, New industries will be created, and some existing ones threatened. How about a moment of silence for the slide rule?

The objective of this book is to teach you the four fundamental tasks of microcomputer interfacing:

- Device select pulse generation

- Microcomputer outputMicrocomputer input

- Interrupt servicing

in the context of 8080-based microcomputers. We hope to give you the basic concepts of microcomputer interfacing and the associated microcomputer I/O programming so that you can develop your own interfaces to other digital devices, including teletypes, crt displays, panel meters, analog-to-digital converters, digital-to-analog converters, laboratory instruments, and the like.

Chapter 1 discusses the future role of microcomputers, the four fundamental tasks of microcomputer interfacing, and summarizes the digital concepts that you will require to make proper use of this book. Chapter 2 describes a small 8080-based microcomputer and discusses the concept of microcomputer input/output in greater detail, especially from the point of view of the use of device select pulses to strobe digital integrated-circuit chips. Chapter 3 provides an introduction to 8080 microcomputer programming. The entire 8080 instruction set is discussed in some detail. Specific attention is focused on data transfer operations, arithmetic and logical operations, branch instructions, input and output instructions, and register decoding. The 8080 instruction set is summarized in a variety of ways.

Chapter 4 treats the very important topic of device select pulse generation. A variety of practical and experimental decoder circuits are provided that can generate one, sixteen, or as many as 256 different device select pulses. Chapter 5 describes an extremely useful technique for counting the number of clock cycles required for the execution of segments of microcomputer programs. The technique permits you to verify the theoretical number of clock cycles for every instruction in the 8080 instruction set. Standard programs are provided that generate

time delays that are multiples of either 0.5 ms or 0.2 s.

Chapter 6, perhaps the most difficult one in this book, provides a description of the internal operation of the 8080 microprocessor chip. The timing behavior of the 8080 is discussed in terms of states, machine cycles, and instruction cycles. Circuits are provided to demonstrate how the IN and OUT control signals can be generated. Chapter 7 discusses the important topic of microcomputer input/output, both the latching of output data and the input of three-state buffered data into the 8080. Circuits and programs are provided that teach you how to detect a specific key on an ASCII keyboard, how to output data to a multiplexed display, and how to log digital data.

Chapter 8 discusses in considerable detail several modes of micro-

Chapter 8 discusses in considerable detail several modes of microcomputer operation, including polled operation and interrupt operation. The subjects of subroutines, interrupts, external flags, masking, the stack, and the strategy of interrupt servicing and priority interrupt software and hardware are all treated. Finally, an appendix summarizes the entire 8080 instruction set with the aid of Intel instruction-byte

diagrams

Basically, this book is a revised and expanded version of an earlier book entitled, The Bugbook III: Microcomputer Interfacing Experiments Using the Mark 80 Microcomputer, an 8080 System, marketed by E&L Instruments, Inc., Derby, Connecticut. Experiments present in the original Bugbook III have been either rewritten as examples, incorporated into the text material, or eliminated. The chapter on interrupts and external flags has been expanded considerably over its previous length. Numerous editorial changes have been made to improve

the clarity of the material.

In this book, we assume that you have a knowledge of the basic concepts of digital electronics, including gates, flip-flops, latches, decoders, multiplexers, three-state and open-collector bussing, memories, shift registers, displays, counters, arithmetic/logic units, and the like. Many such concepts are used in our discussions of microcomputer interfacing. Bugbooks I & II: Logic & Memory Experiments Using TTL Integrated Circuits [E&L Instruments, Inc., 61 First Street, Derby, Connecticut 06418, 706 pages, \$16.95] provide such information. If you wish to interface a microcomputer to a Teletype or crt display, you will need to know some of the basic principles of asynchronous serial digital data communications. To our knowledge, the only book that treats such material in a systematic fashion is Bugbook IIA: Interfacing & Scientific Data Communication Experiments Using the Universal Asynchronous

Receiver/Transmitter (UART) and 20 mA Current Loops [E&L Instru-

ments, Inc., 70 pages, \$4.95].

ments, Inc., 70 pages, \$4.95].

The authors and Dr. Christopher A. Titus are quite active in microcomputer education and system development and design in Blacksburg. Short courses on digital electronics and microcomputer interfacing are available both on an in-house and a scheduled basis from Tychon, Inc. [call (703) 951-9030] or from the Continuing Education Center and Extension Division of Virginia Polytechnic Institute & State University [call Dr. Norris Bell at (703) 951-6328]. To be placed on the mailing list for future Bugbooks on microcomputer programming, analog electronics, and digital electronics, send your name and address to BUGBOOKS, P.O. Box 715, Blacksburg, Virginia 24060.

Finally, we wish to acknowledge the consistent support of Mr. Murray Gallant and E&L Instruments, Inc., in all of our educational efforts in the electronics area.

in the electronics area.

PETER R. RONY DAVID G. LARSEN JONATHAN A. TITUS

# **Contents**

### CHAPTER 1

| What Is a Microcomputer?  Introduction to This Chapter—Objectives—Definitions—Review of Digital Electronics—What Is Useful?—Some Helpful References—Data Processor vs. Microprocessor vs. Microcomputer—Hardware vs. Software—Computer vs. Digital Computer—What Is a Controller?—A Typical 8080 Microcomputer—Test—What Have You Accomplished in This Chapter?       |    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| CHAPTER 2                                                                                                                                                                                                                                                                                                                                                             |    |  |  |  |

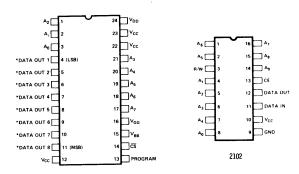

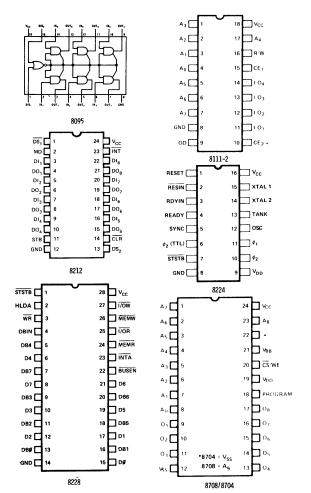

| A SMALL 8080 MICROCOMPUTER  Objectives—Definitions—The 8080 Microcomputer Chip—The 8224 Clock Generator/Driver Chip—An 8080-Based Microcomputer—What Is Interfacing?—What Is an I/O Device?—Uses for Device Select Pulses—Use of a Microcomputer to Strobe Integrated-Circuit Chips—What Have You Accomplished in This Chapter?                                       | 39 |  |  |  |

| CHAPTER 3                                                                                                                                                                                                                                                                                                                                                             |    |  |  |  |

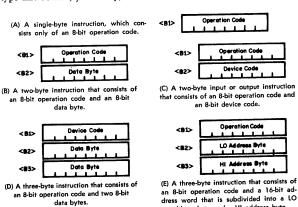

| AN INTRODUCTION TO MICROCOMPUTER PROGRAMMING  Objectives—Definitions—What Is a Computer Program?—What Is an Instruction?—What Is an Operation?—Machine Language—Octal and Hexadecimal Machine Codes—Mnemonic Code—How Do I Go About the Task of Learning Computer Programming—Bit, Byte, Word, and Address—Multibyte Instructions—Instructions vs. Data: How Does the | 93 |  |  |  |

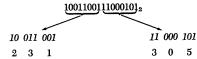

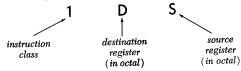

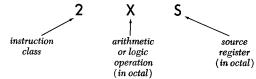

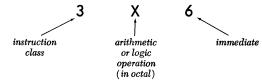

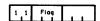

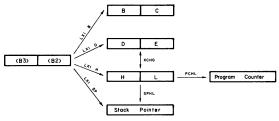

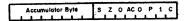

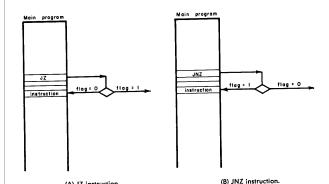

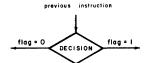

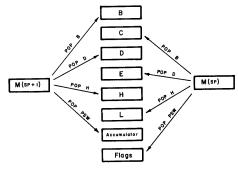

Computer Know?—8080 Microprocessor Registers—What Types of Operations Does the 8080 Microprocessor Perform?—8080 Mnemonic Instructions—Octal/Hexadecimal Listing of the 8080 Instruction Set—An Example of Instruction Decoding—Register Decoding—Arithmetic and Logic Operation Decoding—Immediate Operation Decoding—Branch Operation Decoding—Conditional Branch Instructions—Condition Flag Decoding—Register Pair Decoding—Increment and Decrement Operation Decoding—Data and Memory Addressing Modes—Accumulator Instructions—8080 Instruction Summary—Assembly Language—Machine Language vs. Assembly Language Programs—Introduction to the Examples—Example No. 1—Example No. 2—Example No. 3—Example No. 4—Example No. 5—Example No. 10—Example No. 11—Example No. 12—Test—What Have You Accomplished in This Chapter?

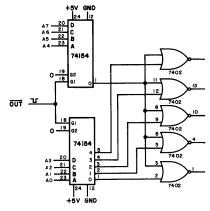

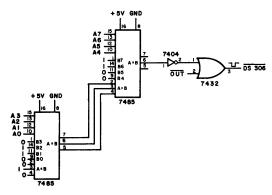

### CHAPTER 4

### CHAPTER 5

### CHAPTER 6

### CHAPTER 7

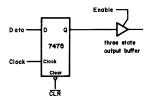

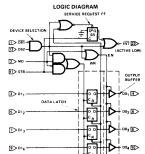

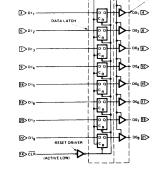

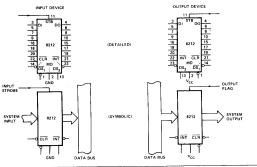

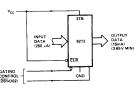

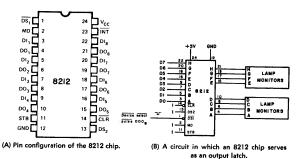

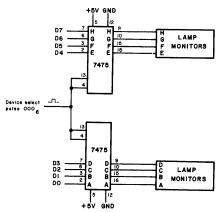

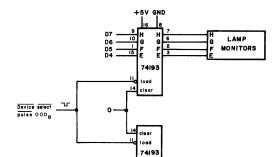

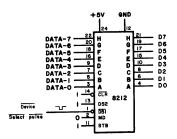

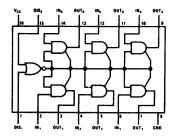

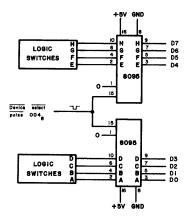

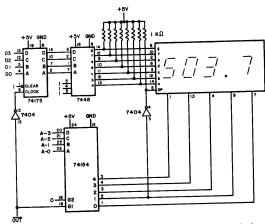

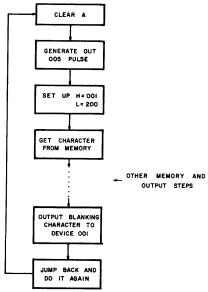

| MICROCOMPUTER INPUT/OUTPUT  Objectives—Definitions—Input/Output—Microcomputer Output Circuits  -Microcomputer Input Circuits—Input/Output Instructions—Input/Output Programs—Microcomputer Output to a Multiplexed Display—Data Logging With an 8080 Microcomputer—What Have You Accomplished in This Chapter?                                                                                                                                                                                                                                                                                                                               | 275   |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|

| CHAPTER 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |  |  |  |

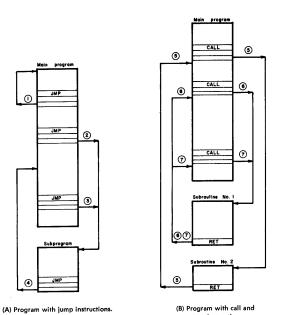

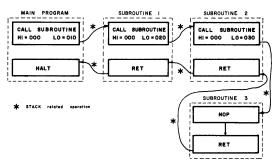

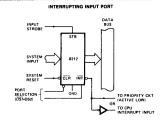

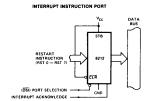

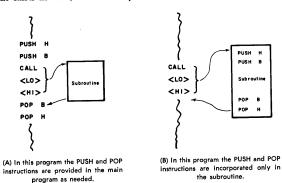

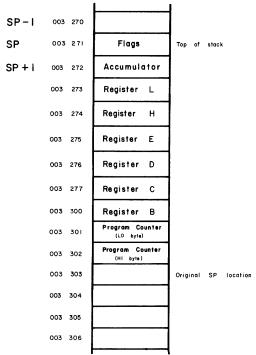

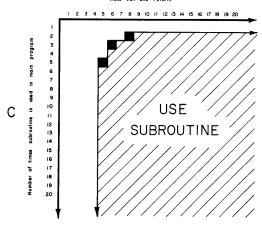

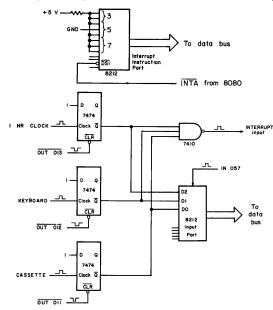

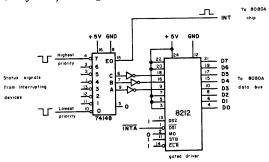

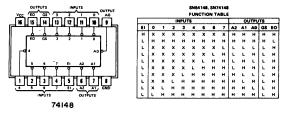

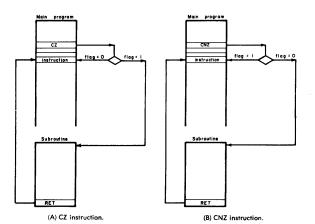

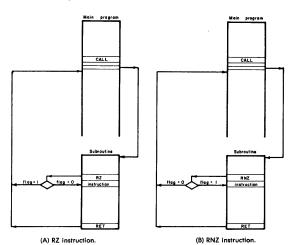

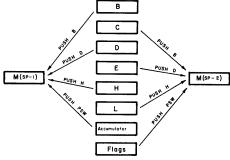

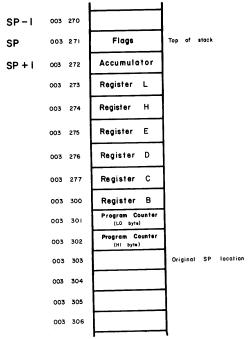

| SUBROUTINES, INTERRUPTS, EXTERNAL FLAGS, AND STACKS  Objectives—Definitions—What Is a Subroutine?—Use of the Stack for Data and Status Storage—When Is a Subroutine Used?—Hardware Integration: SSI, MSI, LSI, and VLSI—Software Integration: SSP, MSP, LSP, and VLSP—The 8080 Subroutine Instructions—The 8080 Stack Instructions—Memory Allocation—Modes of Microcomputer Operation—Basic Types of Interrupts—Enable and Disable Interrupt Instructions—External Flags—Interrupt Mask—Interfacing a Keyboard—Priority Interrupts—Hardware Priority Interrupts—Priority Interrupt Software—Test—What Have You Accomplished in This Chapter? |       |  |  |  |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 349   |  |  |  |

| APPENDIX 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |  |  |  |

| THE 8080A Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |  |  |  |

| APPENDIX 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |  |  |  |

| The 8080 Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 409 |  |  |  |

| Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 411 |  |  |  |

### **CHAPTER 1**

# What Is a Microcomputer?

In this book, you will study real examples that demonstrate the principles, concepts, and applications of an 8-bit microcomputer that is based upon the 8080 microprocessor integrated-circuit chip. In doing so, you will be able to participate in a remarkable electronics revolution in which the computer will be transformed from a large, expensive, and rather esoteric machine into a compact, inexpensive, and common device that will be used by millions of individuals. Before very long, you will find small computers in your home, automobile, lawn mower, office, and perhaps even in some of your recreational equipment. These small computers will be everywhere—millions of them! They will have a profound influence upon everyday life. Already, a cousin of the microprocessor chip, the calculator chip, has essentially made the slide rule obsolete. What has happened with the slide rule will happen with other mechanical devices.

Large computers will continue to perform complicated mathematical calculations, and small hand-held electronic calculators will perform the simpler ones. Since the common view of the computer is as a calculating machine, one might ask: Where does the microcomputer fit? After all, if the large computers do all of the more difficult calculations and the electronic calculators all of the simple ones, is there anything left for the microcomputer to do? The answer to this seeming dilemma resides in the fact that computers have at least two important functions:

As number- and information-crunching machines in which digitally coded information is manipulated at high speeds. As programmable digital controllers that control machines and processes by passing digital signals to and from the computer.

The major use of microcomputers will be as controllers, not as information-crunching machines. We could estimate the possible market for microcomputers if we knew how many machines that could be controlled by a microcomputer exist per capita in the United States. The telephone could use a microcomputer, as could an electric type-writer, a television set, a sophisticated child's game, a stereo set, a dishwasher, an electric range, a clothes washer, etc. When one includes homes, offices, industry, and laboratories, there may be between three and ten machines or devices per capita that can be automated with the aid of microcomputers. With 200 million individuals in the U.S., this translates to 600 million to 2 billion microcomputers. The market, for electronic calculators may be no more than 100 million, which is still a large number.

The subject of computers is vast, and a series of textbooks can be written to cover the general scope of computer architecture, operation, and applications. This is not the intention with this book, which differs from most texts written on computers in the respect that the primary emphasis will be on the use of a computer as a controller rather than as a number-crunching machine. You will learn how to *interface* a microcomputer, where the word "interface" means the joining of the microcomputer to an instrument, device, or machine in a way such that both operate in a compatible and coordinated fashion. You will focus your attention only on a computer built around an 8080 microprocessor chip. The reasons for doing so are as follows:

- Based upon the number of manufacturers who are or will be manufacturing the 8080 microprocessor chip, it is likely that 8080-based microcomputers will be very common.

- 2. By the end of 1977, the 8080 microprocessor chip will probably be sold at a price of \$10 in quantities of one, and even less for considerably larger quantities. Such a low price should ensure the popularity of 8080-based microcomputers.

- The 8080 microprocessor instruction set is quite powerful. Programs are relatively easy to write.

- 4. The 8080 microprocessor is relatively fast. It can execute an arithmetic instruction such as add or subtract in only 2 μs. With improvements in the state of the art, even faster 8080 chips are now available.

- An 8080 microcomputer can directly access up to 65,536 different 8-bit memory locations and can generate 256 different input strobe signals and 256 different output strobe signals.

<sup>\*</sup>See Appendix 1 for references in the text denoted by superscripts.

Owing to the popularity of the 8080 chip, a wide variety of programs will be readily available.

Thus the authors believe that your time will best be spent learning the principles, concepts, and applications of a computer of the future, such as the 8080, rather than a computer of the past, such as the PDP-8.

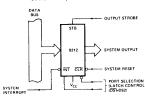

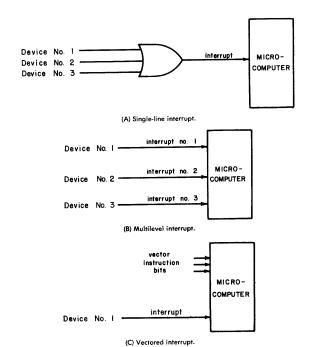

This book is concerned with the four fundamental tasks of computer interfacing:

- 1. The generation of device select signals.

- 2. The latching of output data.

- 3. The acquisition of input data.

- 4. The servicing of interrupt signals.

An extensive series of examples will provide you with the concepts and techniques necessary for developing your own circuits and the writing of your own programs to accomplish one or more of the four fundamental tasks. Once you have mastered these tasks, the world of microcomputer controls will be yours.

### INTRODUCTION TO THIS CHAPTER

In the chapters that follow this one, you will encounter a series of examples that will help you to develop competence in *microcomputer* interfacing. Before you do so, however, it would be useful for you to develop an understanding of what a computer is and what the distinctions are between *microcomputers*, *minicomputers*, *computers*, *controllers*, *data processors*, and *logic processors*.

In addition, it would be useful for you to gain some insight into the characteristics of the principal "bug" in this book, the 8080 microprocessor chip. This chip, first marketed by Intel Corporation in 1974, is a complete 8-bit parallel central processing unit (CPU), also abbreviated MPU, that is fabricated on a single LSI chip. Simple instructions can be performed in as little as 2 µs, which compares to the 1.2-µs instruction time for similar operations in the Digital Equipment Corp. PDP-8/E minicomputer. The 8080 chip is being "second sourced" by Texas Instruments, Inc., National Semiconductor Corp., NEC, and several other chip manufacturers. Such actions signify that the semiconductor industry is betting that the 8080 will become an important force in the microprocessor market.

Any discussion of the 8080 can be subdivided into the following topics:

- The pin configuration and pin functions of the 8080 chip.

- The organization of a typical microcomputer that employs the 8080 chip.

- The internal operation of the 8080 microprocessor.

- The instruction set of the 8080 microprocessor.

Starting in this chapter and continuing in several chapters, we shall discuss each of these topics. The detail with which we shall do so will vary from topic to topic. The objective is not to bombard you with a fusillade of timing diagrams and machine cycle descriptions, but rather to help you develop the skills that you will need to use an 8080-based breadboard microcomputer system.

For the interested reader, the authors recommend the following sources for additional information on the characteristics and operation of the 8080 chip:

- Robert H. Cushman, "The Intel 8080: First of the second-generation microprocessors," Electronic Design News 19 (9), p. 30 (May 5, 1974).

- Masatoshi Shima and Federico Faggin, "In switch to n-MOS, microprocessor gets a 2-µs cycle time," Electronics 47 (8), p. 95 (April 18, 1974).

- Intel Corp., Intel Intellec 8/Mod 80 Microcomputer Development System Reference Manual, Santa Clara, California, 1975.

- Intel Corp. Intel 8080 Microcomputer System Manual, Santa Clara, California, September, 1976.

- Adam Osborne, An Introduction to Microcomputers. Volume II. Some Real Products, Osborne Associates, Berkeley, California, 1976.

- Adam Osborne, 8080 Programming for Logic Design, Osborne Associates, Berkeley, California, 1976.

- W. J. Weller, A. V. Shatzel, and H. Y. Nice, Practical Microcomputer Programming. The Intel 8080, Northern Technology Books, 1976.

### **OBJECTIVES**

At the end of this chapter, you will be able to do the following:

- Explain the difference between a microprocessor and a micro-

- Define the terms: computer, digital computer, data processor, controller, hardware, software, memory, memory word, memory address, memory data, read, write, random access memory, read-only

- memory, interfacing, device select pulse, and interrupt.

Describe different types of computers and controllers on the basis of the following characteristics: word length, complexity, application, cost, memory size, program, speed constraints, input/output, design, and manufacturing volume.

• Describe the operation of a typical 8080 microcomputer system.

### MICROPROCESSORS AS MICROCONTROLLERS AND LOGIC PROCESSORS

Microprocessor applications tend to fall into the following categories:

Table 1-1. The Spectrum of Computer-Equipment Complexity, from Simple Hard-Wired Logic Systems to High-Performance General Data Processing Equipment. This Table Is Based on Pro-Log Corp. Material and Is Adapted From an Article by Wallace B. Riley in the October 17, 1974, Issue of Electronics.

| Word Length<br>(Bits)           | -                                     | 7                       | 4           | æ                        | 16                 | 32                                     | 2                                                      |

|---------------------------------|---------------------------------------|-------------------------|-------------|--------------------------|--------------------|----------------------------------------|--------------------------------------------------------|

| Complexity                      | Hard-Wired                            | Programmed              | Calculator  | Microprocessor           | Minicomputer       | Large (                                | Large Computer                                         |

| Application                     | a a a a a a a a a a a a a a a a a a a | Control                 | <u> </u>    | Dedicated<br>Computation | ed<br>tion         | Low-Cost<br>General<br>Data-Processing | High-Performance<br>General<br>Data Processing         |

| \$5<br>0<br>0<br>0<br>0<br>0    | Under<br>\$100<br>(1974)              |                         |             | \$1000<br>(1974)         |                    | \$10,000<br>(1974)                     | \$100,000<br>and Up<br>(1974)                          |

| Memory Size                     | Very Small<br>0-4 Words               | Small<br>2-10 Words     | II<br>/ords | Medium<br>10-1000 Words  | Lan<br>1000–1 Mill | Large<br>1000–1 Million Words          | Very large<br>More Than<br>1 Million Words             |

| Program<br>Speed<br>Constraints | Read-Only<br>Real Time                | Slow                    | 3           | Medium                   | E                  |                                        | Reloadable<br>Throughput-<br>Oriented                  |

| Input-Output                    | Integrated                            | Few Simple<br>Devices   | mple<br>ces | Some Complex<br>Devices  | omplex<br>es       |                                        | Roomful of<br>Equipment                                |

| Design                          | Logic                                 | Logic +<br>Microprogram | -+<br>ogram |                          | Microp             | Microprogram<br>Macroprogram           | Macroprogram<br>High-Level Language<br>Software System |

| Manufacturing<br>Volume         | Large                                 | ·                       | į           |                          |                    |                                        | Small                                                  |

- Controllers

- Consumer products

- Communications

- Terminals

- Microcomputers

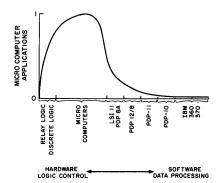

Each of these categories is discussed in some detail in the *Microprocessor Handbook*.<sup>3</sup> As shown in Table 1-1 and Fig. 1-1, microprocessor applications fall between relay logic and discrete random logic (gates and flip-flops) on one hand and inexpensive minicomputers such as the LSI-11 and PDP-8/A on the other. Microcomputers fabricated from microprocessors are not as sophisticated as some of the popular minicomputers and cannot easily perform data processing problems. They are simply not set up at this moment to run FOR-TRAN, COBOL, or other high-level languages. The computer power inherent in many of today's 8-bit and 16-bit microcomputers would allow them to do so, but the software support is simply not yet available for them.

At the moment, it would be more appropriate to call systems constructed from microprocessor chips by the terms microcontrollers or logic processors. They are excellent programmable sequencers, and can process logic data and make decisions upon such data. Thus, they can sequence events in response to decisions upon input data.

### WHERE MICROCOMPUTERS FIT

Fig. 1-1. Applications foreseen for microcomputers. Microcomputers will carve out their own niche between discrete logic and inexpensive minicomputers.

When it was first introduced, the Intel 8080 microprocessor chip sold for \$360 in quantities of one. By the end of 1977 the price should drop to \$10 in quantities of one. The price of a piece of equipment containing such a microprocessor will then reflect primarily the mechanical aspects of the equipment, i.e., the housing and electromechanical devices.

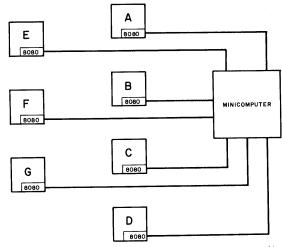

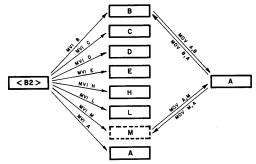

In this book the emphasis is on control and logic processing applications. The authors don't foresee many 8080-based microcomputers being tied to \$5000 worth of input/output equipment and used in competition with the PDP-11 and competitive minicomputers. Rather, we foresee minicomputer-microcomputer hierarchies in which one to ten instruments and devices containing 8080 chips are all tied to a single minicomputer. An example of such a computer hierarchy is shown in Fig. 1-2. Instruments A through G all communicate directly to the much larger minicomputer through an 8080-based microcomputer contained within each instrument. The instruments are controlled by the 8080 computers, and the minicomputer oversees such control and logs important instrument parameters. The minicomputer might also pro-

Fig. 1-2. An example of a computer hierarchy. The individual instruments or machines A through G are controlled by built-in 8080 microprocessors. These microprocessors also communicate back and forth with the minicomputer, which monitors the operation of the entire system.

vide the microcomputer control set points at the beginning of each day. Each microcomputer might contain only 2K to 8K of memory, whereas the minicomputer might have a minimum of 16K or 32K of memory to permit it to handle a higher-level language such as FORTRAN or APL. Please keep in mind that future microcomputers will be quite inexpensive, perhaps no more than several hundred dollars for a complete microcomputer system. The more venturesome individuals in the electronics industry predict full microcomputer systems for a cost of \$10 to \$20 in quantities of 100. At such prices, microcomputers will be everywhere.

### **DEFINITIONS**

accumulator—The register and associated digital electronic circuitry in the arithmetic unit of a computer in which arithmetic and logical operations are performed.

bidirectional-Responsive in opposite directions.4

bidirectional data bus-A data bus in which digital information can be

transferred in either direction.

bus-A path over which digital information is transferred, from any of several sources to any of several destinations. Only one transfer of information can take place at any one time. While such transfer is taking place, all other sources that are tied to the bus must be disabled.

clock-(a) Any device that generates at least one clock pulse, or (b) a timing device in a system that provides a continuous series of timing

pulses.4

computer-Any device, usually electronic, capable of accepting information, comparing, adding, subtracting, multiplying, dividing, and integrating this information, and then supplying the results of these processes in acceptable form. The major elements of a computer usually include memory, control, arithmetic, logical, and input and output facilities.4

computer interfacing—The synchronization of digital data transmission between a computer and one or more external input/output devices. controller—An instrument that holds a process or condition at a desired

level or status as determined by comparison of the actual value with the desired value.4

data processor-A digital device that processes data. It may be a computer, but in a larger sense it may gather, distribute, digest, analyze, and perform other organization or smoothing operations on data. These operations, then, are not necessarily computational. Data processor is a more inclusive term than computer.2

device select pulse-A synchronization pulse generated by a computer to synchronize the operation of a specific input or output device.

digital computer—An electronic instrument capable of accepting, storing and arithmetically manipulating information, which includes both data and the controlling program. The information is handled in the form of coded binary digits (0 and 1) represented by dual voltage levels.<sup>6</sup>

digital controller—A controller that acquires the actual value of the condition in digital form and compares it to the desired value contained within the controller. If there is any difference between the two, a digital signal is sent out by the controller to reduce this dif-

ference

direct address—An address that specifies the location within memory of an instruction or data byte.

external device addressing—A device name, expressed as a digital code, that is generated by the CPU to address a specific external device. Both input and output devices can be addressed.

fixed-program computer—A computer in which the sequence of instructions is permanently stored or wired. The computer program is not subject to change either by the computer or the programmer except by rewiring or changing the storage input.<sup>5</sup>

general-purpose computer—A computer designed to solve a large variety of problems; a stored-program computer which may be adapted

to any of a large class of operations.5

hardware—The mechanical, magnetic, electronic, and electrical devices from which a computer or computer system is fabricated; the assembly of material forming a computer system.<sup>2</sup>

input/output, input-output—General term for the equipment used to communicate with a computer and the data involved in the communication.<sup>5</sup>

interfacing—The joining of members of a group (such as people, instruments, etc.) in such a way that they are able to function in a com-

patible and coordinated fashion.1

interrupt—In a computer, a break in the normal execution of a computer program such that the program can be resumed from that point at a later time. The source of the interrupt can be external or internal.

memory—Any device that can store logic 1 and logic 0 bits in such a manner that a single bit or group of bits can be accessed and retrieved 10

memory address—The storage location of a memory word.

memory cell—A single storage element of memory, capable of storing one bit of digital information.

memory data—The memory word occupying a specific location in memory, or the memory words collectively located in memory.

memory word—A group of bits occupying one storage location in a computer. This group is treated by the computer circuits as an en-

tity, by the control unit as an instruction, and by the arithmetic unit as a quantity. Each bit is stored in a single memory cell.

microcomputer—A fully operational computer system based upon a microprocessor chip.

microcontroller—A small controller, most likely one based upon a microprocessor chip.

microprocessor—A single integrated-circuit chip that contains at least 75 percent of the power of a very small computer.

monostable multivibrator—A circuit having only one stable state, from which it can be triggered to change the state, but only for a predetermined interval, after which it returns to the original state.

programmable read-only memory—A read-only memory that is field programmable by the user.<sup>10</sup>

pulser-A logic switch that generates a clock pulse.

random access memory—A semiconductor memory into which logic 0 and logic 1 states can be written (stored) and then read out again (retrieved).<sup>10</sup>

read—To transmit data from a memory to some other digital device.

read-only memory—A semiconductor memory from which digital data can be repeatedly read out, but cannot be written into, as is the case for a random access memory.<sup>10</sup>

software—The totality of programs and routines used to extend the capabilities of computers, such as compilers, assemblers, narrators, routines, and subroutines.<sup>5</sup>

special-purpose computer—A computer designed to solve a specific class or narrow range of problems.<sup>5</sup>

stored-program computer—A computer capable of performing sequences of internally stored instructions, usually capable of modifying those instructions as directed by the instructions.<sup>5</sup>

volatile memory—In computers, any memory which can return information only as long as power is applied to the memory. The opposite of nonvolatile memory.

wired-program computer—A computer in which nearly all instructions are determined by the placement of interconnecting wires held in a removable plugboard. This arrangement allows for changes of operations by simply changing plugboards. If the wires are held in permanently soldered connections, the computer is called a fixed-program type.<sup>4</sup>

write—To transmit data into a memory from some other digital electronic device. A synonym is store.

### REVIEW OF DIGITAL ELECTRONICS: WHAT IS USEFUL?

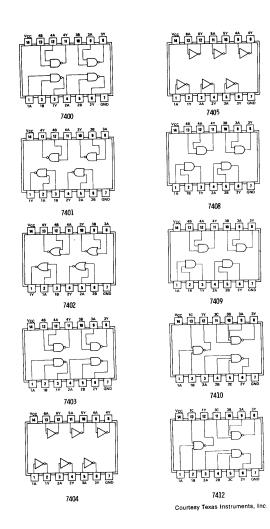

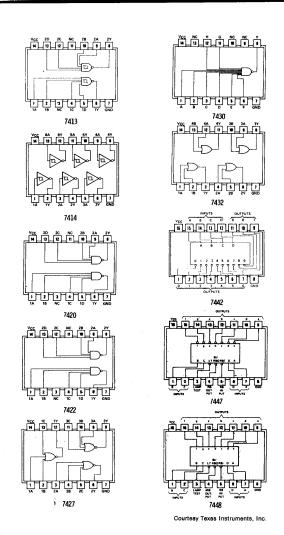

Two previous Bugbooks, Bugbooks I and II: Logic & Memory Experiments Using TTL Integrated Circuits, provide the background

that you will need to use for this book. Some of the more important chips and digital concepts that you should understand include the fol-

- The logic operations and, or, nand, nor, and exclusive or.

- The gating characteristics of the four basic logic gates: AND, NAND, or, and nor.

- The 7400, 7402, 7408, and 7432 integrated-circuit chips.

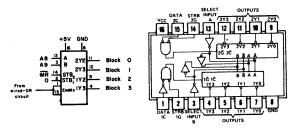

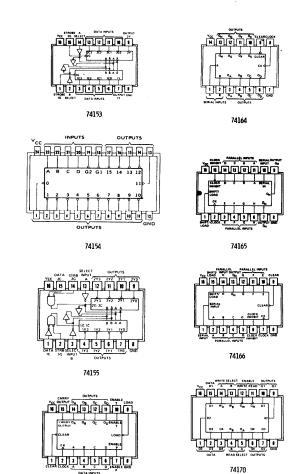

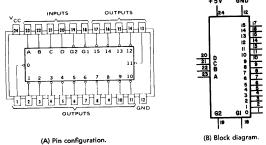

- Decoders, especially the 7442 four-line-to-ten-line and the 74154 four-line-to-sixteen-line integrated-circuit chips.

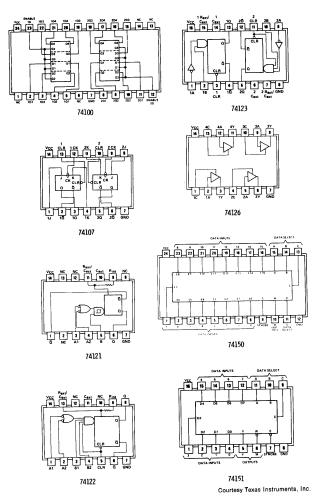

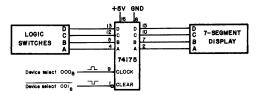

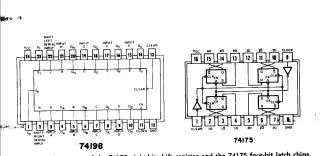

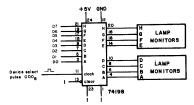

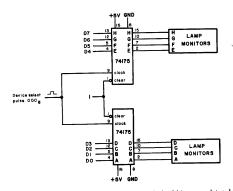

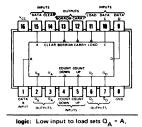

Latches, including the 7474, 7475, 74100, 74175, 74192, 74193, and

- 74198 integrated-circuit chips. The 74192 and 74193 chips are counters, and the 74198 chip is an 8-bit shift register.

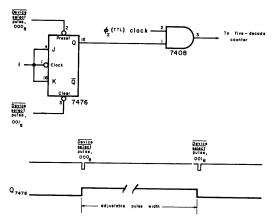

J-K flip-flops, including the 7470, 7473, 7476, and 74106 integrated-

- circuit chips.

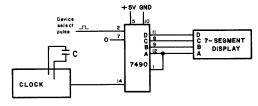

- Counters, including the 7490, 7493, 74192, and 74193 integratedcircuit chips.

- Three-state bussing.

- Input/output devices such as logic switches, pulsers, clocks, lamp monitors, and seven-segment LED displays.

The terms strobe, enable, and disable.

- Monostable multivibrators, such as the 74121, 74122, 74123, and 555 integrated-circuit chips.

- Clocked logic.

- Registers, including the 74198 8-bit shift register.

- Arithmetic operations, such as addition and subtraction, and the use of carry bits in binary systems.

• Multiplexing, including the 74153 four-line-to-one-line multiplexer.

- The function of strobe or chip enable inputs on 7400-series integrated-circuit chips.

- Binary, binary-coded decimal, octal, hexadecimal, and ASCII codes.

### SOME HELPFUL REFERENCES

While the authors would like to discuss the subjects of computers, minicomputers, and microcomputers in great detail, they will not be able to do so owing to the limitations of space in this chapter. For those readers who are interested, the following books are recommended. They approach the subject of computers in ways that are quite useful to the novice:

- 1. The Value of Power, General Automation, Inc., 1055 South East Street, Anaheim, California 92805, 1973.

- An excellent paperback book that describes the characteristics of minicomputers. May be out of print.

2. Douglas Lewin, Theory and Design of Digital Computers, John Wiley & Sons, Inc., New York, 1972.

A more advanced book. The author pays particular attention to the jargon in the field of digital computers.

3. David Hagelbarger and Saul Fingerman, CARDIAC: A Cardboard Illustrative Aid to Computation, Bell Telephone Laboratories, Inc.,

A 52-page Bell System Educational Aid that presents a simplified view of what a computer is. Very well written, and quite useful for teaching purposes.

4. The Microprocessor Handbook, Texas Instruments, Inc., P. O. Box 5012, Dallas, Texas 75222.

A nicely written text that provides you with a good overview of micro-processor applications, architecture, and chip fabrication technologies. Worth having.

5. D. J. Woollons, Introduction to Digital Computer Design, McGraw-Hill, Inc., New York, 1972.

A more advanced book, one that becomes more useful as you develop

an understanding of computers and computer operation.

6. A series of six texts: (1) Binary Arithmetic, (2) Microcomputer Architecture, (3) The 4-Bit Microcomputer, (4) The 8-Bit Microcomputer, (5) Assemblers and Prototyping Systems, and (6) 8-Bit Assemblers and Compilers, Iasis, Inc., 770 Welch Road, Suite 154 ED, Palo Alto, California 94304.

At \$124.50 for the set of six books, this material is only for the wealthy

among you. They are quite well written and worth having. Very little

affiong you. They are quite went written and worth having. Very index information on interfacing is provided, however.

7. Jules Finkel, Computer Aided Experimentation: Interfacing to Minicomputers, John Wiley & Sons, Inc., New York, 1975.

Provides general descriptions of the various facets of minicomputer interfacing, but lacks details. Does not describe UARTs, RS-232C, 20-mA current loops, or microprocessors.

8. Intel 8080 Microcomputer Systems User's Manual, Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051, July

If you are working with the 8080 microprocessor chip, you must have this reference manual. Individual chapters include the following:

Chapter 1. The Functions of a Computer Chapter 2. The 8080 Central Processing Unit

Chapter 3. Interfacing the 8080

Chapter 4. Instruction Set Chapter 5. 8080 Microcomputer System Components

Standard CPU Interface

RAMs

I/O

Peripherals Coming soon Chapter 6. Packaging Information

9. An Introduction to Microcomputers, Volume 1: Basic Concepts, Adam Osborne and Associates, Inc., P. O. Box 2036, Berkeley, California 94702.

An excellent book at a very reasonable price.

- 10. 8080 Programming for Logic Design, Adam Osborne and Associates, Inc., P. O. Box 2036, Berkeley, California 94702. Another excellent book.

- 11. Software Design for Microprocessors, Texas Instruments, Inc., Dallas, Texas 75222.

Describes software associated with the different TI microcomputer systems. Section 5.2 provides a description of a badge-reading system based upon the 8080 microprocessor chip.

### DATA PROCESSOR VS. MICROPROCESSOR VS. MICROCOMPUTER

It is difficult to find a good definition for the term digital computer. The perspective on what is a computer given by Donald Eadie in his book Introduction to the Basic Computer is quite appealing

"This chapter serves as a general introduction to the field of digital devices, with particular emphasis on those devices called computers, or more properly, data processors. The name data processor is more inclusive because modern machines in this general classification not only compute in the usual sense, but also perform other functions with the data which flow to and from them. For example, data processors may gather data from various incoming sources, sort it, rearrange it, and then print it. None of these operations involves the arithmetic operations normally associated with a computing device, but the term computer is often applied anyway.

"Therefore, for our purpose a computer is really a data processor. Even such data processing operations as rearranging data may require simple arithmetic such as addition. This explains why a certain amount of imprecision has entered our language and why confusion exists between the terms computer and data processor. The two terms are so loosely used at present that often one has to inquire further to determine exactly what is meant."2

Eadie thus defined the term data processor as follows:

data processor-A digital device that processes data. It may be a com-

puter, but in a larger sense it may gather, distribute, digest, analyze, and perform other organization or smoothing operations on data.

### Comments

This program requires an 8-bit output latch and display to permit you to observe the results of the arithmetic and logical operations that you perform on the accumulator contents. Refer to the circuits described in Chapter 7.

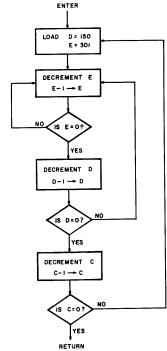

The subroutine starting at HI = 000 and LO = 100 generates time delays ranging from 0.200 second to 51.2 seconds through variations in the timing byte for register C at LO memory address 005.

If you execute the program as it stands, you will observe that the output display quickly fills up with logic 1's, starting from right to left. At memory addresses 011 through 015, you have five program bytes with which you can perform different types of accumulator operations. Thus, with the program segment:

| 011 | 076 | MVI A | Load the following byte into the                                     |

|-----|-----|-------|----------------------------------------------------------------------|

| 012 | 360 | 360   | accumulator  Data byte corresponding to the                          |

| 013 | 346 | ANI   | binary word 11110000 <sub>2</sub> And the data that follows with the |

| 014 | 252 | 252   | contents of the accumulator  Data byte corresponding to the          |

| 015 | 000 | NOP   | binary word 10101010 <sub>2</sub> No operation                       |

you should observe that the AND operation between the byte 11110000 and the byte 10101010 produces the logical result 10100000, an operation that proceeds bit by bit. By changing the logical instruction at LO=013, you can demonstrate the behavior of the or and exclusive-or instructions on the same initial data.

If you execute the following program segment contained within the main program:

| 011 | 074 | INR A | Increment the contents of the accu- |

|-----|-----|-------|-------------------------------------|

|     |     |       | mulator by one                      |

| 012 | 067 | STC   | Set the carry flag to logic one     |

| 013 | 077 | CMC   | Complement the carry flag           |

| 014 | 047 | DAA   | Decimal adjust the accumulator      |

| 015 | 000 | NOP   | No operation                        |

you should observe a decimal output count from 0 to 99 on the output display. The  $\bf 047$  instruction is the decimal adjust accumulator instruction, which converts the result of adding two bcd numbers in binary back to a pair of packed bcd numbers. It is  $\it not$  a binary-to-bcd conversion instruction as such.

### EXAMPLE NO. 10

### Purpose

The purpose of this example is to demonstrate the BCD Input and Direct Conversion to Binary Routine, which is No. 80-147 in the Intel

"In short, if a minicomputer is a 1-horsepower unit, the microprocessor plus supporting circuitry is a ¼-hp unit. But as LSI technology improves, it will become more powerful. Already single-chip bipolar and CMOS-on-sapphire processors are being developed that have almost the capability of the minicomputer."

### HARDWARE VS. SOFTWARE

$\it Hardware$  and  $\it software$  are important terms that will be used repeatedly in this chapter. It is appropriate, therefore, to define them early.

hardware—The mechanical, magnetic, electronic, and electrical devices from which a computer is fabricated; the assembly of material forming a computer.<sup>2</sup>

software—The totality of programs and routines used to extend the capabilities of computers, such as compilers, assemblers, narrators, routines, and subroutines. Contrasted with hardware.<sup>5</sup>

The specific 8080-based microcomputer ssytem that you will use, along with any integrated-circuit chips, wire, breadboarding aids, and peripheral devices, are all considered to be the hardware. The programs and subroutines that you use and write are the software. In this book, you will first develop hardware skills in interfacing an 8080-based microcomputer. Once you acquire such skills, you will then develop software skills that will allow you to apply your hardware interfacing capability to a variety of instruments and machines. As you gain experience with microcomputers, you will learn that it can often take considerable amounts of time to write microcomputer programs that contain hundreds of program steps.

### COMPUTER VS. DIGITAL COMPUTER

It is instructive to define the terms computer and digital computer. Good definitions are difficult to find, as was mentioned previously.

computer—Any device, usually electronic, capable of accepting information, comparing, adding, subtracting, multiplying, dividing, and integrating this information, and then supplying the results of these processes in acceptable form. The major elements of a computer usually include memory, control, arithmetic, logical, and input and output facilities.<sup>4</sup>

A device capable of accepting information, applying prescribed processes to that information, and supplying the results of these processes. It usually consists of input and output devices, storage, arithmetic and logical units, and a control unit.<sup>5</sup>

digital computer-An electronic instrument capable of accepting, storing, and arithmetically manipulating information, which includes both data and the controlling program. The information is handled in the form of coded binary digits (0 and 1), represented by dual voltage levels.6

A computer which processes information represented by combinations of discrete or discontinuous data as compared with an analog computer for continuous data. A device for performing sequences of arithmetic and logical operations, not only on data but its own program. A stored program digital computer capable of performing sequences of internally stored instructions, as opposed to such calculators as card-programmed calculators, on which the sequence is impressed manually.

An electronic calculator that operates with numbers expressed directly as digits, as opposed to the directly measurable quantities (voltage, resistance, etc.) in an analog computer.<sup>4</sup>

Several subsidiary definitions include the following:

fixed-program computer-Computer in which the sequence of instructions are permanently stored or wired. The computer program is not subject to change either by the computer or the programmer except by rewiring or changing the storage input.<sup>5</sup>

general-purpose computer-Computer designed to solve a large variety of problems; a stored program computer which may be adapted to any of a very large class of operations.5

special-purpose computer-A computer designed to solve a specific

class or narrow range of problems.5

stored-program computer-A computer capable of performing sequences of internally stored instructions, usually capable of modifying those instructions as directed by the instructions.<sup>5</sup>

wired-program computer-A computer in which instructions that specify the operations are specified by the placement and interconnection of wires. Wires are usually held by a removable control panel, allownently wired machines which are then called fixed-program computers.  $^5$ ing flexibility of operation, but the term is also applied to perma-

A computer in which nearly all instructions are determined by the placement of interconnecting wires held in a removable plugboard. This arrangement allows for changes of operations by simply changing plugboards. If the wires are held in permanently soldered connections, the computer is called a fixed-program type.4

### WHAT IS A CONTROLLER?

Graf has defined a controller as follows:

controller—An instrument that holds a process or condition at a desired level or status as determined by comparison of the actual value with the desired value.<sup>4</sup>

Controllers can be analog or digital, and can be electronic, mechanical, or even pneumatic, or perhaps some combination of these. A digital controller acquires the actual value of the condition in digital form and compares it to the desired value contained within the controller. If there is any difference between the two, a digital signal is sent out to the device, machine, or process to initiate actions to reduce this difference. The digital controller itself consists either of integrated-circuit chips and discrete components that are hard-wired to a printed-circuit board, or else a computer of any size with a limited number of chips to serve as an interface between the computer and the external world.

The question of cost becomes an important factor when one considers the use of computers as controllers. One would not control 100 devices, each with a value of \$500, with a \$1,000,000 computer; the use of such a large computer to control \$50,000 worth of equipment is a form of overcontrol. On the other hand, such a computer would be useful in the control of a \$20,000,000 chemical plant. It would appear that one could justify the cost of a computer controller if it represents only a modest percentage of the cost of operating a process or producing a product. The tradeoffs in costs constantly change as the prices of computers decrease. With the advent of microcomputers, the costs of controlling equipment should decrease.

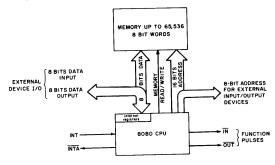

### A TYPICAL 8080 MICROCOMPUTER

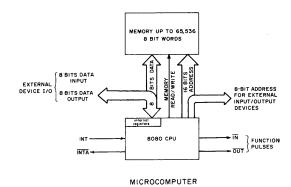

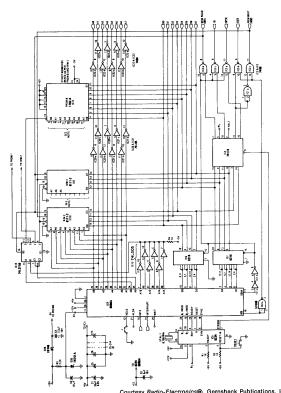

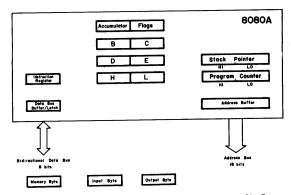

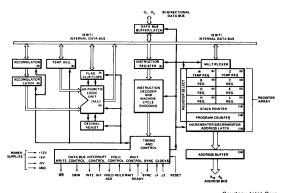

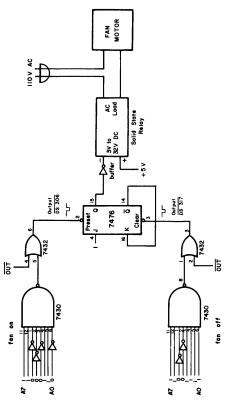

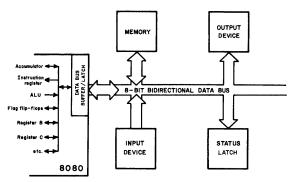

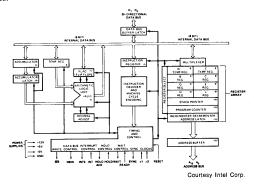

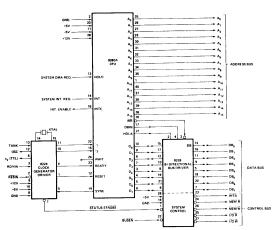

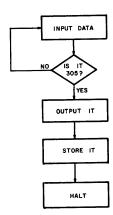

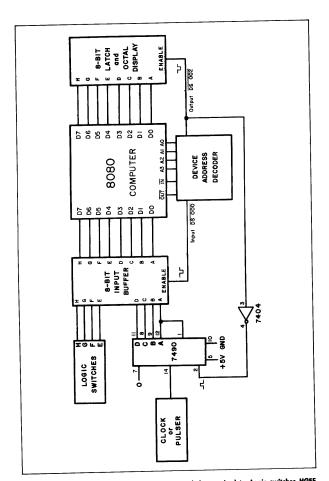

A typical microcomputer constructed from the 8090 chip is shown in Fig. 1-3. This microcomputer processes all of the minimum requirements for a computer. For example:

- It can input and output data.

- It contains an arithmetic/logic unit (ALU), located within the 8080 chip, that performs arithmetic and logical operations.

- It contains "fast" memory (the authors believe that speed is an important requirement for a functional computer these days).

- It is programmable, with the data and program instructions capable of being arranged in any sequence desired.

- It is digital.

Fig. 1-3 shows the important data paths of the microcomputer. In the sections below, we shall dissect this diagram and discuss the individual naths

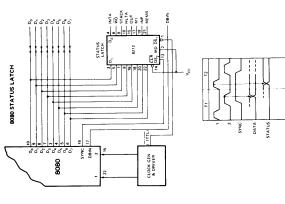

Fig. 1-3. A typical 8080 microcomputer system, in which the significant data paths are shown

### Memory

Consider first the data communication between the 8080 central processing unit (CPU) and memory. You will require some definitions, which will be useful in the ensuing discussion:

memory—Any device that can store logic 1 and logic 0 bits in such a manner that a single bit or group of bits can be accessed and retrieved 10

memory address—The storage location of a memory word.

memory cell—A single storage element of memory.

memory data—The memory word occupying a specific storage location in memory, or the memory words collectively located in memory.

memory word—A group of bits occupying one storage location in a computer. This group is treated by the computer circuits as an entity, by the control unit as an instruction, and by the arithmetic unit as a quantity. Each bit is stored in a single memory cell.

programmable read-only memory (PROM)-A read-only memory that

is field programmable by the user.10

read/write memory—A semiconductor memory into which logic 0 and logic 1 states can be written (stored) and then read out again (retrieved). 10 Sometimes called RAM.

read-only memory (ROM)—A semiconductor memory from which digital data can be repeatedly read out, but cannot be written into, as in the case for read/write memory.<sup>10</sup>

read—To transmit data from a memory to some other digital electronic device.

volatile memory.—In computers, any memory that can return information only as long as power is applied to the memory. The opposite of nonvolatile memory.<sup>4</sup>

write—To transmit data into a memory from some other digital electronic device. A synonym is store.

The 8080 microprocessor employs 8-bit words that are stored in memory and are addressed with a 16-bit memory address bus. With a quick calculation, we conclude that there exist  $2^{16} = 65,536$  different memory locations that can be accessed by the microprocessor. This access to memory is direct, which means that you don't have to engage in any special tricks or digital electronic gimmicks to access any given memory location within the 65,536 possible locations. Forty-pin integrated-circuit chips do have their advantages, and having one pin for each of the sixteen address lines is one of them. The total memory capacity of the 8080 microprocessor is known in the trade as 64K. This is far more memory than you will ever need for most applications, but it is nice to know that you have such power in reserve.

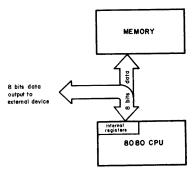

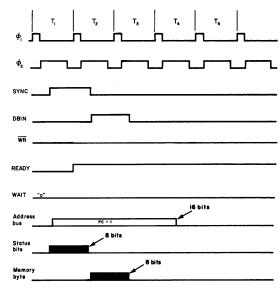

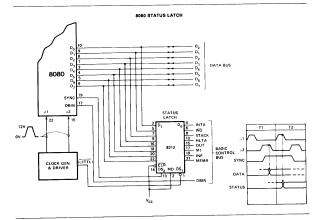

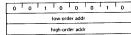

A given memory location is addressed with the aid of a 16-bit memory address bus that is shown in Fig. 1-3. It takes only 1  $\mu$ s to accomplish such addressing. The memory address bus is shown in Fig. 1-4. Data is transferred between the 8080 CPU and memory over 8-bit

Data is transferred between the 8080 CPU and memory over 8-bit data input and data output busses, both of which are shown in Fig. 1-3 and Fig. 1-5. In most recent 8080 microcomputers, these two busses are combined into a single 8-bit bidirectional data bus. By input, we mean input into the CPU. By output, we mean output from the CPU. The point of reference is always the CPU. Data leaving the CPU is

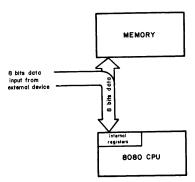

Fig. 1-4. The 16-bit memory address bus between the 8080 CPU and memory.

Fig. 1-5. Data transfer between the 8080 CPU and memory. In most 8080 systems there is a single bidirectional data bus.

always considered to be *output data*; data entering the CPU is always *input data*. In some cases, the input and output data are transferred between the *accumulator* and memory. The term *accumulator* is defined in the following way:

accumulator—The register and associated digital electronic circuitry in the arithmetic unit of a computer, in which arithmetic and logical operations are performed.

Data can also be transferred to other internal registers within the 8080 chip. A register is defined as:

register—A short-term digital electronic storage circuit, the capacity of which is usually one computer word.<sup>4</sup>

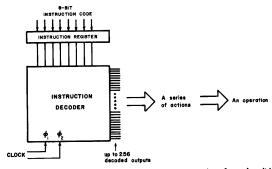

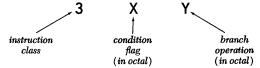

Other registers, besides the accumulator register, include the *instruction register*, from which the decoding of the instruction occurs; six general-purpose registers, which are classified by the letters B, C, D, E, H, and L; a program counter register; a stack pointer register; and at least three temporary registers to which you have no access. All of these registers are discussed in subsequent chapters. They are pointed out here so that you will not get the false impression that data from memory is only transferred to the accumulator register. The authors regard the accumulator register to be the heart of the entire microcomputer: Arithmetic and logic operations are always performed to or on the eight bits of data present within the accumulator. For extracted, and, ored, or compared to the contents of the accumulator register. It is not possible to add the contents of one memory location to the contents of another memory location. You must always proceed

in such additions through the accumulator register. The accumulator register is also important because all input and output data passes through the accumulator whenever you use the two computer instructions IN and OUT.

Between the 8080 CPU and memory there exists a single output line, shown in Fig. 1-3, called memory read/write. When this line is at logic 1, you are able to read data into the CPU either from memory or from an external device. When this line is at logic 0, you are able to write data from the CPU into memory or an external output device. In some systems separate read and write lines are used.

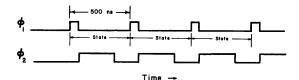

As a final point, you can employ any type of "fast" digital electronic memory device, including read/write (R/W) memory, read-only memory (ROM), and programmable read-only memory (PROM). "Fast" memory means simply that the memory can perform either a read or a write operation during a single microcomputer instruction. A typical 8080 microcomputer system operates at a clock rate of 2 MHz, and a read or write operation takes only 650 ns. Thus, R/W memory, ROM, and PROM all need an access time of 650 nanoseconds to allow you to take full advantage of the maximum clock speed. Slower semiconductor memories can be employed, but the microcomputer will have to "wait" while a read or write operation takes place.

### Data Outpu

The 8-bit output data bus between the 8080 CPU and memory also serves as the output data bus to an external output device. This is shown in Figs. 1-3 and 1-6.

Fig. 1-6. Data transfer between the 8080 CPU and an output device.

When you output data to an external device, there are several important requirements that you must meet:

- You must select the specific output device that will receive eight bits of data from the accumulator register in the CPU.

- You must indicate to this device the precise instant of time when output data is available on the output data bus.

• The device must "capture" or "latch" this output data in a very

- short period, typically 500 ns.

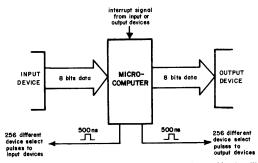

All three of the preceding requirements are accomplished at the same time with a single output pulse, which is generated by the 8080 chip with the aid of some extra digital circuitry external to the 8080 chip. We call such a pulse a device select pulse. It synchronizes the 8080 CPU and the output device so that when the CPU is ready to provide output data, the output device is ready to receive it. Keep in mind that the microcomputer is operating at a clock rate of 2 MHz. Each computer instruction is executed in a very short period, which ranges from  $2 \mu s$  to  $9 \mu s$ . Thus, accumulator data designated as *data output* is not available for very long. You must capture this data within 500 ns, or else it will disappear. We cannot emphasize enough how important this rapid "capture" of output data is to the successful operation of a complete microcomputer system that includes input/output devices. We will consider these points in greater detail when we discuss the topic of microcomputer interfacing in this chapter. If you are interested in how the function pulse OUT, which is used to generate device select pulses, is created by the 8080 microcomputer, please jump to the section titled "Machine Cycle Identification" in Chapter 6.

### **Data Input**

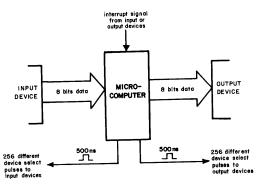

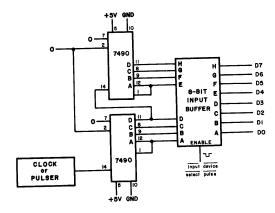

The 8-bit input data bus between the 8080 CPU and memory also serves as the input data bus from an external input device. This is shown in Figs. 1-3 and 1-7. The basic considerations that apply to data output also apply to data input. Thus:

- You must select the specific input device that will transmit eight bits of data to the accumulator register within the CPU.

- You must indicate to this device the precise instant of time when the input data bus is ready to acquire the input data and transfer it to the accumulator register.

- The accumulator register must "capture" this data in a very short period, typically 500 ns.

All three of these tasks are accomplished at the same time with a single output pulse, which is generated by the 8080 chip with the aid of some extra digital circuitry external to the chip. Such a pulse is also called a device select pulse. It synchronizes the 8080 CPU and the input

Fig. 1-7. Data transfer between an input device and the 8080 CPU.

device so that when the CPU is ready to receive input data, the input device is ready to transmit it.

### Other Input/Output Techniques

There is an alternative and very exciting technique for transferring data directionally between the microcomputer general-purpose registers B, C, D, E, H, and L and an input/output device. The technique is called memory mapped I/O and the chips used are in a family of interface chips recently marketed by Intel Corporation and others. Included in this family is the 8255 programmable peripheral interface chip, which turns an input/output device into a pseudo-memory location that is addressed not with an IN or OUT instruction, but rather with memory instructions such as MOV, STA, LDA, and the like. The advantage of doing so is the savings of several microseconds per 8-bit data transfer. The computer programming may be easier as well. This technique is particularly well adapted for the acquisition or transfer of blocks of data in short intervals of time. We will not discuss the technique to any degree in this book.

### **External Device Addressing**

External device addressing can be defined as the use of computer software to generate input/output synchronization pulses, called device select pulses, to synchronize the transfer of data between the CPU and an external input or output device. This is one of the most important tasks of microcomputer interfacing, and must be learned well.

The basic objective of external device addressing is to generate a single unique clock pulse at a precise instant of time to a specific ex-

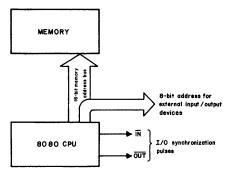

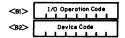

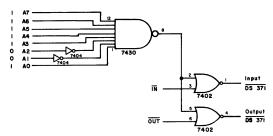

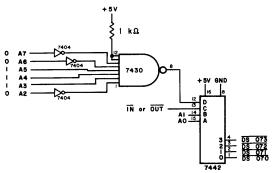

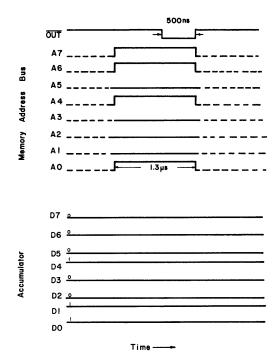

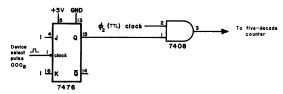

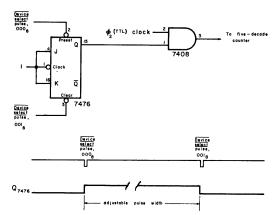

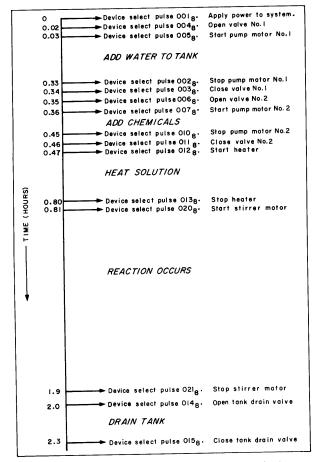

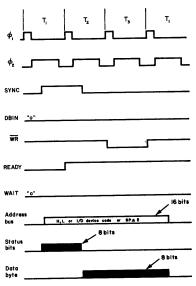

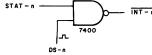

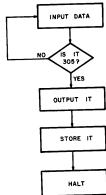

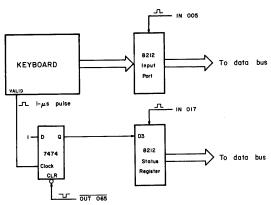

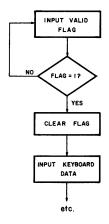

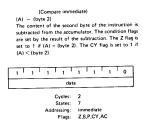

ternal input or output device. The clock pulse can either be a positive or negative clock pulse. With the 8080 microcomputer, negative clock pulses are generated most easily. This is done by decoding an 8-bit device code that appears for about 1.5  $\mu$ s on the memory address bus and using an I/O function or synchronization pulse, called  $\overline{\text{IN}}$  or  $\overline{\text{OUT}}$ , that appears for 500 ns during the 1.5- $\mu$ s interval associated with the 8-bit device code. The two function pulses and the 8-bit address for external I/O device addressing are shown in Figs. 1-3 and 1-8.

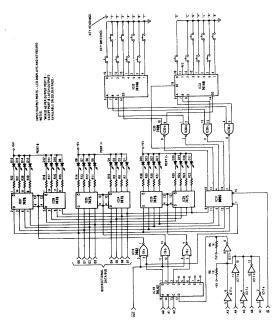

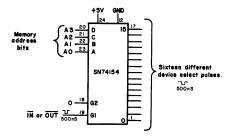

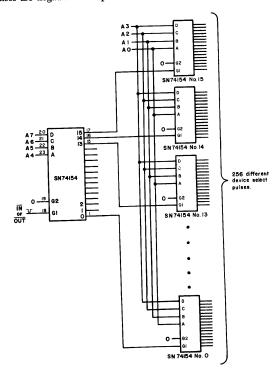

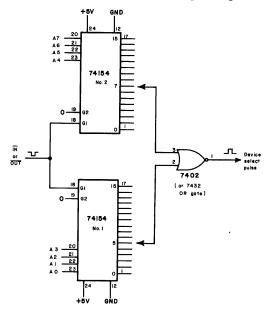

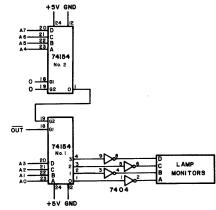

The details of how individual device select pulses are generated are provided in Chapter 4. Briefly, here is how this is done. The computer instructions for transferring data between the accumulator and input/output devices specify the specific device desired. For an output computer instruction, you have your choice of any one device among 256 different devices. The same is true for the input computer instruction. Thus, you have the ability to address, i.e., send device select pulses to, 256 different input devices and 256 different output devices. How is this done? Each input or output computer instruction contains an 8-bit device code. We can calculate that an 8-bit binary number can specify  $2^8 = 256$  different devices. We use a pair of 4-line-to-16-line decoder chips, such as the 74154 decoder, to decode the 8-bit device code into a single output pulse. Seventeen 74154 decoders can generate 256 different pulses, as will be shown in Chapter 4. The remaining details can be discussed with the aid of Fig. 1-9.

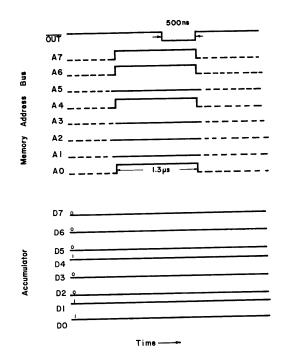

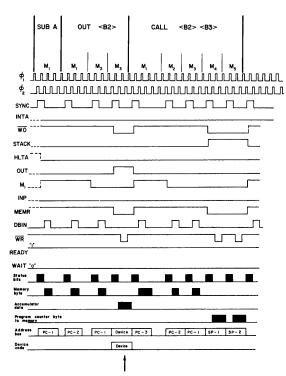

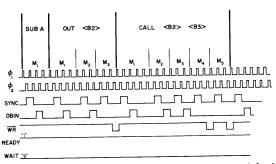

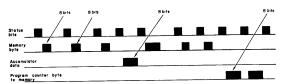

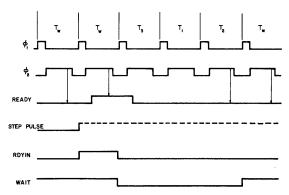

Fig. 1-9 provides timing diagrams for the accumulator register contents, the memory address bus, and the OUT pulse that is generated

Fig. 1-8. During an 8080 input or output instruction, the 8-bit device code appears on the address bus, and an 1/O synchronization pulse appears on the control bus. Such signals are used to gate the transfer of input/output data.

Fig. 1-9. Timing diagram indicating the logic states existing on the memory address bus, within the accumulator, and at the OUT signal line during an OUT instruction.

by the OUT computer instruction and some digital circuitry external to the 8080 chip. Note the following:  $\frac{1}{2} \frac{1}{2} \frac{$

- The accumulator register contents are available for at least several microseconds, and perhaps much longer.

The 8-bit device code appears at the eight least-significant bits of the 16-bit memory address bus for a period of 1.3 µs. In the figure, the device code is 11010001<sub>2</sub>, or 321<sub>8</sub> in octal code.

The OUT synchronization pulse lasts for only 500 ns. It is during this 500 ns that data is transferred between the accumulator register and the output device.

- ister and the output device.

Both the 8-bit device code and the  $\overline{OUT}$  synchronization pulse are connected to 74154 decoders to generate a single device code for device 321<sub>8</sub> for a period of only 500 ns. Thus, the use of the term, "capture," is entirely appropriate for data transfers between the accumulator and input/output devices.

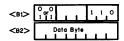

The input of eight bits of data to the accumulator with the aid of an IN computer instruction proceeds along lines similar to those shown in Fig. 1-9. The only difference is that you should substitute the term buffer data for accumulator and  $\overline{\text{IN}}$  for  $\overline{\text{OUT}}$  in the figure. The transfer of data to the accumulator occurs in only 500 ns.

### Interrupt Servicing

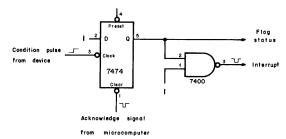

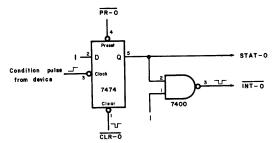

The final data path that we shall discuss is associated with the technique of *interrupt servicing*. The term *interrupt* can be defined in the following way:

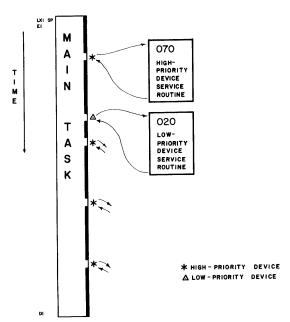

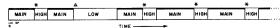

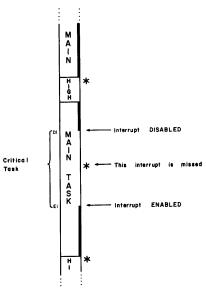

interrupt—In a computer, a break in the normal execution of a computer program such that the program can be resumed from that point at a later time. The source of the interrupt can be internal or external

The important question is: Why would we want to interrupt program execution? The answer is that this is the most efficient way to operate a microcomputer or, for that matter, any computer. Until an external input/output device requests assistance, or "servicing," from the microcomputer, it is most efficient for the microcomputer to completely ignore the device. In fact, the microcomputer can be programmed so that it ignores all input/output devices; it idles in a "wait loop" while it waits for an interrupt signal from one of the devices. If many I/O devices require servicing at essentially the same time, the microcomputer has a protocol in hardware or software and knows which device is the most important. It will assign a priority to each device, and will always service the higher-priority devices first.

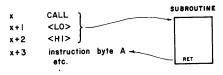

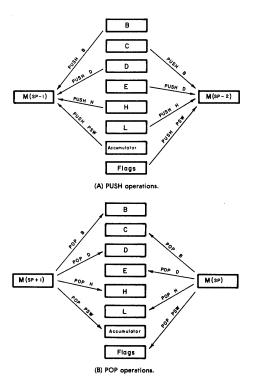

When a program interrupt is generated, the following sequence of events usually occurs:

- The computer stores the memory address of the instruction following the one that it is currently executing.

- The computer stores any temporary information—flags, the contents of the accumulator register, and the contents of other registers—that may be important when the interrupted program resumes operation.

- The computer goes to a well-defined location within memory and executes a series of program steps to "service" the interrupting device.

4. Once it has finished "servicing" the device, the computer recalls the temporary information and returns to the program step following that step at which the interrupt occurred.

This is similar to what you would do if you were interrupted while reading this book. You would mark your place, remember any special information, and then devote your attention to the "interrupt." After servicing the interrupt, you would restore the remembered information, locate the bookmark, and continue reading.

If more than one input/output device requires servicing, the microcomputer must make a decision which one to handle first. Once it has made this decision, it remembers which remaining devices have generated the interrupt requests, and then procedes to the service subroutine.

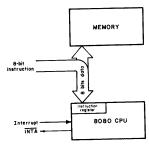

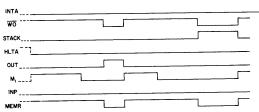

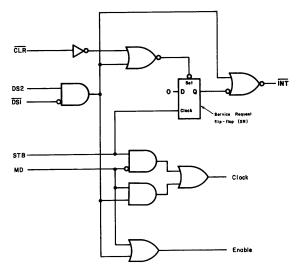

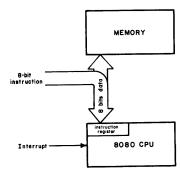

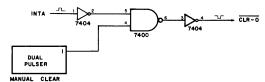

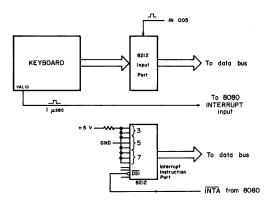

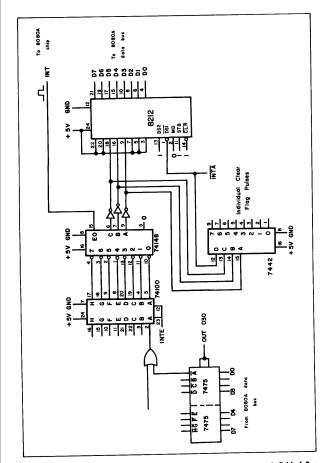

In the 8080 microcomputer, an 8-bit instruction is jammed into the CPU at the time of the interrupt to tell the computer where to go in memory to "service" the interrupt. Only eight different memory addresses are provided for this purpose, certainly not a large number. There are a variety of tricks that can be employed to handle interrupts. The schematic diagram shown in Fig. 1-10 indicates the important signals during an interrupt request: an interrupt pulse, an interrupt acknowledge control signal,  $\overline{\text{INTA}}$ , and an 8-bit instruction that is jammed into the instruction register.

### TEST

This test probes your understanding of the microcomputer and digital electronic concepts described in this chapter. Please write your answers on a separate piece of paper.

Fig. 1-10. On receiving an <u>"interrupt"</u> request, the 8080 CPU generates an "interrupt acknowledge" control signal, INTA, that is used to gate an 8-bit instruction into the instruction register within the CPU.

- 1-1. Explain the difference between a microprocessor and a microcomputer.

- 1-2. Draw a diagram and show the important data paths in a typical 8080based microcomputer.

- 1-3. What are the minimum requirements for a computer circa 1977?

- 1-4. List and describe the four fundamental tasks of computer interfacing.

- 1-5. In your own words, define the following terms:

data processor controller bus accumulator flag memory address memory cell memory word hardware software read write computer interfacing interrupt device select pulse clock bidirectional data bus read/write memory read-only memory (ROM)

Your performance on this test will be acceptable if you can answer all of the above questions correctly in a 90-minute closed-book examination. You will repeatedly encounter the above concepts in this book.

## WHAT HAVE YOU ACCOMPLISHED IN THIS CHAPTER?

It was stated in the introduction to this chapter that at the end you would be able to do the following:

- Explain the difference between a microprocessor and a microcomputer.

- A microprocessor is a single IC chip, whereas a microcomputer is a fully operational computer system. This distinction has been discussed, with quotes from the literature, early in this chapter.

- Define the terms: computer, digital computer, data processor, controller, hardware, software, memory, memory word, memory address, memory data, read, write, read/write memory, read-only memory, interfacing, device select pulse, and interrupt.

Definitions for these terms have been provided in this chapter.

- Describe the operation of a typical 8080 microcomputer system.

This was done in modest detail. You should be able to do as well. Focus upon the signal lines and data paths within the system.

## **CHAPTER 2**

# **A Small 8080** Microcomputer

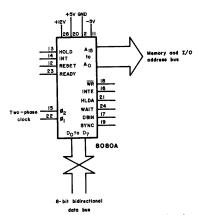

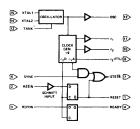

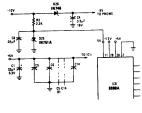

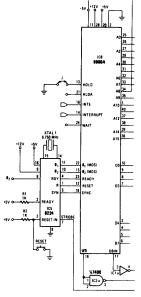

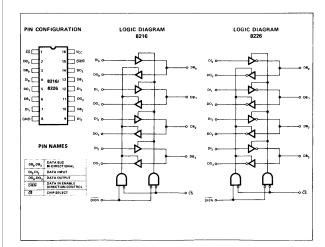

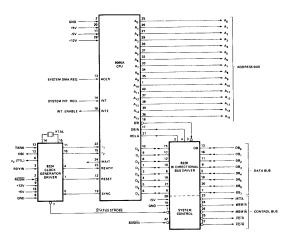

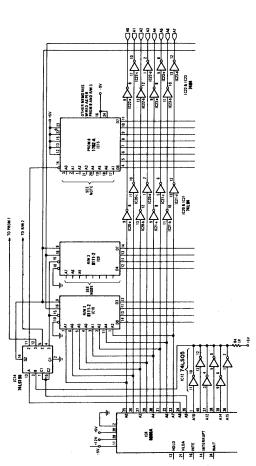

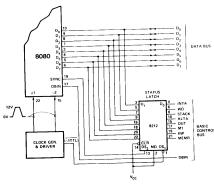

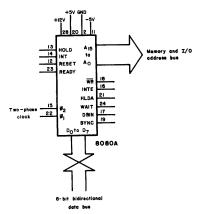

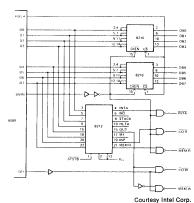

In this chapter, you will see how an 8080 (or 8080A) microprocessor In this chapter, you will see how an 8080 (or 8080A) microprocessor chip can be used to configure a small 8080-based microcomputer. We will examine the signals entering and leaving the 8080 chip, how auxiliary chips such as the 8224 are used to control the operation of the microcomputer, and the development of the address, data, and control buses, which are vital in interfacing applications. The microcomputer has been previously described in the May, June, and July, 1976, issues of Radio-Electronics magazine. You may refer to these articles for additional details on the assembly and operation of the microcomputer. ditional details on the assembly and operation of the microcomputer.

## **OBJECTIVES**

At the end of this chapter, you will be able to do the following:

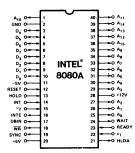

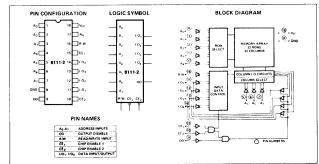

- Identify the memory address bus, data bus, control inputs, control outputs, and power inputs on the 40-pin 8080A microprocessor

- Describe the function of each pin on the 8080A microprocessor chip.

- Describe in some detail the various component sections of a small 8080A microcomputer system.

• List the general principles of computer interfacing that apply to

- most digital computers.